Issues with the I²C (Inter-IC) Bus and How to Solve Them

Contributed By DigiKey

2018-08-09

The Inter-Integrated Circuit bus is very well known as it is widely used in many devices by numerous IC manufacturers. Additionally, there is a lot of information available on the Internet. Nevertheless, there are always issues and questions surrounding the Inter-IC bus, starting with the correct way to abbreviate it. Fortunately, the official logo provides the answer, I²C.

This technical article will discuss some common issues that can occur using the I²C bus and how to solve them. The fundamentals on how the I²C bus works are not part of this article, but can be found in this tutorial: I²C Bus Fundamentals.

The most common issues when using the I²C bus are conflicts addressing the slaves, mixing different bus speed and/or voltage level devices, wrong or forgotten pull-up resistors, excessive bus capacitance, and no common ground connection.

Addressing

Devices attached to the I²C bus receive their data after being addressed. Addresses on the I²C bus can be 7 or 10 bits long, and are predefined in the device. The addresses are assigned by NXP to the device manufacturers. Each device attached to the bus should have a unique address.

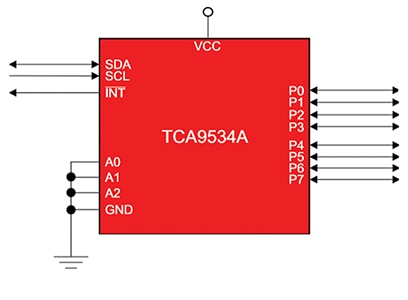

To use the same device more than once per I²C bus, many devices offer the ability to change the address within a predefined range by pulling pins to the supply voltage or to ground. For example the TCA9534APWR I/O expander from Texas Instruments.

This device can be configured with three address lines (A0, A1 and A2) for the addresses ranging from 0x38 to 0x3F (Table 1), allowing 8 devices to be used on the bus.

|

||||||||||||||||||||||||||||||||||||||||

Table 1: Address Reference (Image source: DigiKey)

For example, pulling all three address lines low assigns the address 0x38 to the TCA9534A as shown in Table 1.

Figure 1: TCA9534 configured for address 0x38 (Image source: Texas Instruments)

Some devices are only available with one address. For example, the STS21 from Sensirion AG or the SI705x from Silicon Labs, cannot be configured with different addresses. If more than one of these devices are used on the same bus, it will cause issues as the devices will all respond at the same time, possibly crashing the entire bus.

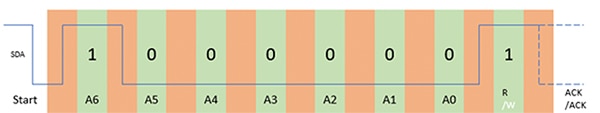

Another more typical issue with addressing the devices attached to the I²C bus is software related. The I²C bus is an 8-bit serial bus. The address is typically 7 bits long, followed by a bit to designate a read or write. For example, reading from the address 0x40 (0b01000000) would produce a 0x81 (0b10000001) on the bus, as shown in Figure 2 below. The eighth bit is a 1 for reading and a 0 for writing.

Figure 2: A read from address 0x40 as seen on SDA (Image source: DigiKey)

A 10-bit address uses two bytes on the I²C bus. The first 5 bits are always 0b11110, followed by the two most-significant bits and the 8th bit again the read/write bit. The second transferred byte contains the 8 least significant bits of the 10-bit address. Reading from the 10-bit address 0x240 (0b1001000000) would create the two bytes 0xf5 (0b11110101) and 0x40 (0b01000000).

The 7-bit addresses 0x70 thru 0x7B are reserved for 10-bit addressing, and can’t be used by 7-bit devices. This enables the possibility to mix 7-bit and 10-bit devices on the same I²C bus.

Using a logic analyzer that supports the I²C bus, software addressing issues can easily be found and resolved. Note that some I²C bus logic analyzers show the transferred address directly.

Bus speed

I²C bus devices are available in different speeds. As defined in the I²C specification, the different bidirectional speeds are Standard mode (Sm) with a bit rate up to 100 kbit/s, followed by Fast mode (Fm) up to 400 kbit/s, Fast mode Plus (Fm+) up to 1 Mbit/s, and finally High-speed mode (HS) that reaches up to 3.4 Mbit/s. As they are typically downwards compatible, the higher speed devices can be used on the same bus with lower speed devices at the lower data rate. Conversely, if a lower speed device were connected to a faster speed bus, it could result in an unpredictable state and block the bus.

Voltage levels

While mismatched speeds can block the bus, mixing different voltage levels can be catastrophic and literally destroy parts.

According to the I²C specification, the voltage levels for the high and low signal are defined relative to the supply voltage. The table below shows the min and max voltage levels for 2.5 volts up to 5 volts. Note that a 2.5 volt device is unable to produce sufficient voltage for a 5 volt device to interpret as a high.

|

Table 2: Input Voltage Levels (Table source: DigiKey)

Vice versa, a 5 volt output could possibly destroy a 2.5 volt device.

Bus segmentation

Segmenting the I²C bus could solve the issues of the different voltage levels, different data rates, and even devices with the same address.

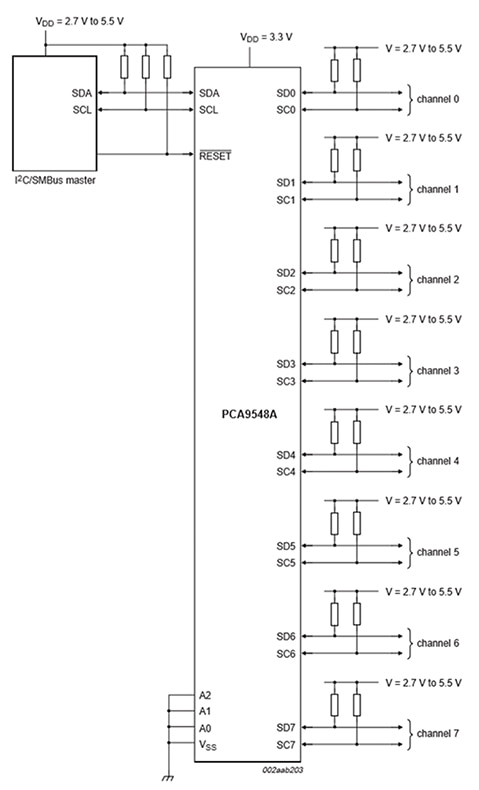

Segmenting the I²C bus is possible by using bus switches like the PCA9548APW,118 from NXP USA Inc., or the PCA9548ADWR from Texas Instruments. By programming these devices, it’s possible to enable or disable different segments from accessing the bus. Different segments can be split by voltage level, speed, or devices with the same address.

Figure 3: I²C bus switch (Image source: NXP)

When working with different voltage levels, the different segments can be active at the same time. For the same address, however, it must be ensured that segments with the same address are not active at the same time. Of course, the bus switch also has to support the different voltage levels and/or speed modes. While the two devices shown above support voltages of 1.8 V, 2.5 V, 3.3 V and 5 V, as well as speeds up to Fast mode at 400 kbit/s, this is not always enough.

The PCA9617ADPJ from NXP USA Inc. is a bus repeater that supports speeds up to Fm+, and voltages down to 0.8 V on one side and 2.2 V on the other. This device can be used to either extend the range, or to separate one side from the other using its enable line. As this device does not act as an I²C slave, it needs an additional pin from the microcontroller to separate the bus lines.

Finding switches or repeaters supporting speeds up to Fm+ bus is more difficult than finding a similar solution for a high-speed bus. For a single master bus, the easiest solution would be to select a processor similar to the SAM D21 Family from Microchip Technology that offers two or more I²C busses, and separate the devices by speed. For a multi-master system, the solution is slightly more complicated. One of the masters would need to use a bridge mode that would forward every signal with the speed up to Fm+ to the other bus, but separates the busses when switched to Hs mode.

Bus capacitance

Separating the bus into different segments helps with additional issues such as bus line capacitance because the maximum capacitance is separate for each segment. Every device attached to the bus lines adds to the existing capacitance caused by the circuit board traces. A higher bus capacitance results in slower rise and fall times as it needs to be charged/discharged from the gates. Adding numerous devices to the same I²C bus can reach the specified limit, slowing down communication.

Not only do too many devices increase the bus capacitance, the same happens for bus lines that are too long. I²C was designed to be a bus between integrated circuits on a single PCB. However, it’s often used to communicate with devices on a different PCB over a cable distance reaching some feet. For the traces on the PCB, many design tools offer the possibility to calculate the trace capacitance. For standard ribbon cables, this value is typically given in the datasheet as a capacitance per foot of 10 to 15 pF. Additionally, having the bus travel over several feet of cable to different PCBs can result in a noisy signal caused by EMI, which can also lead to communication failure.

Common ground

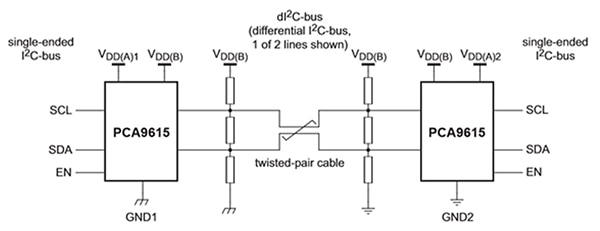

For I²C it is important to have a common ground connection between all devices on the bus. Due to power consumption, the ground levels on boards connected by a few feet of cable can be different, causing communication issues. An option to avoid this and also reduce possible EMI issues is the PCA9615DPJ from NXP USA Inc. This device is an I²C bus repeater with a standard I²C bus on one side, and a differential I²C bus on the other.

Figure 4: Differential I²C bus (Image source: NXP)

The differential signal not only reduces the possible EMI issues, but also eliminates the need for a common ground connection. It also allows the I²C bus to be extended for a twisted pair cable length up to ten feet for a multi-drop bus with a 1 MHz clock speed (Fm+ bus), and even longer for lower speeds.

Pull-up resistors

Lastly, but possibly most important are the pull-up resistors.

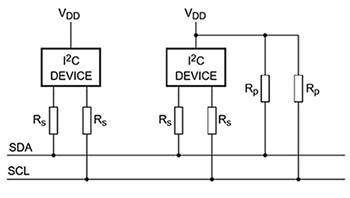

All of the attached ports on the I²C bus are open drain, allowing the use of different voltages on the bus lines. The voltage thresholds are defined by the voltage the lines are pulled up to with the resistors. Each segment of the I²C bus requires pull-up resistors, and the values can differ for each segment. Some devices provide internal pull-up resistors that can be enabled or disabled. Whether it’s practical to use them needs to be decided on a case by case basis.

A low value resistor pulls the SDA and SCL lines strongly to the maximum bus voltage, which could render some bus devices incapable of pulling the line down to the specified low voltage level. Also, the resistance of the bus line will add to the pull-up resistance, and devices closer to the pull-ups may have a different voltage level than ones further away. Conversely, choosing a pull-up resistor that is too high will result in a longer rise time, which will also be dependent on the bus capacitance of the wire, traces, connections, and pins present on the bus.

How can the resistor value be determined?

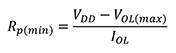

The I²C Specification provides two formulas for calculating the minimum and maximum resistance for the pull-up resistor.

The minimum resistance Rp(min) depends on the bus voltage VDD and the low-level output current IOL. VOL(max) is either 0.4 volts, or 0.2 VDD for VDD below 2 volts.

|

Table 3: Minimum pull-up resistor values for different supply voltages (Table source: DigiKey)

Using a lower resistance than the values shown in the table would result in a higher current through the device which could damage it, or result in an unclear status for the low signal.

The maximum resistance Rp(max) is calculated with the estimated bus capacitance Cb and the maximum rise time tr. The maximum rise time is dependent on the data rate of the bus.

![]()

The table below shows the allowed maximum resistance (Rp(max)) for the maximum rise time (tr(max)) and maximum bus capacitance (tr(max)) for the different bus speeds. To obtain a lower rise time, either the bus capacitance or the resistor value needs to be reduced.

|

Table 4: Maximum resistor value for worst case bus (Table source: DigiKey)

The table above shows the worst-case scenarios with the maximum bus capacitance and maximum rise time for the different bus speeds. The best option is to estimate the bus capacitance and calculate the resistance value with the provided formula.

It is very important to keep the pull-up resistor between the calculated minimum and maximum values. It is, however, still possible to have resistor values that are too high. One reason could be that series resistors used to protect the devices were not included in the calculation. Note that such series resistors will also affect the rise and fall time of the bus.

Figure 5: Pull-up and series resistors on the I²C bus (Image source: NXP)

In general, should unstable communication issues arise, it’s recommended to measure the rise and fall time, and adjust the pull-up resistors accordingly.

A real-world example

The Arduino Uno uses internal pull-up resistors which are specified between 20 kΩ to 50 kΩ. This allows for a maximum bus capacitance between 7 pF and 18 pF for Fm bus speed, and between 24 pF and 59 pF for Sm bus speed.

With each port on the bus having a capacitance of up to 10 pF along with some additional capacitance for wiring and connections, the Arduino could have communication issues using Fm bus speed with even a single slave device. Sm bus speed, however, might work with up to a few devices. As such, when using I²C on the Arduino, it is recommended to use external pull-up resistors.

Conclusion

By using devices with the same speed and voltage, selecting appropriate pull-up resistors, and with good planning on address usage, many common issues with I²C can be avoided.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.