Analog Basics - Part 3: Pipeline ADCs and How to Use Them

Contributed By DigiKey's North American Editors

2020-07-14

Editor’s Note: Analog-to-digital converters (ADCs) connect the analog to the digital world and so are a fundamental component of any electronic system that connects to the real world. They are also a key determining factor of a system’s performance. This series explores the fundamentals of ADCs, their various types, and their application. Part 1 discusses SAR ADCs; Part 2 discusses delta-sigma (ΔƩ) converters; and here, Part 3 discusses the features, characteristics, and usage of pipeline ADCs. Part 4 shows how delta-sigma ADCs can generate ultra-low noise results. Part 5 explores difficult input driving issues for SAR ADCs.

Some of the applications that ADCs service are ultra-high-speed multi-carrier cellular infrastructure base stations, telecommunications, digital predistortion observations, and backhaul receivers—all of which edge towards requiring ADCs that sample in the gigasample-per-second region. Part 1 and Part 2 of this analog basics series discuss successive approximation register (SAR) and delta-sigma (ΔƩ) ADCs, respectively, and how to apply them in appropriate applications. However, neither technology is up for the challenge of producing gigasamples per second (GSPS) results.

For example, the SAR ADC uses a “snapshot” algorithm and so its speed is limited to 10 megasamples per second (MSPS) due to its serial approach. In the case of the high-resolution ΔƩ ADC’s oversampling algorithm, this requires additional time to acquire and average multiple samples that create 24-bit output data rates up to 5 megahertz (MHz). GSPS rates are profoundly outside the sampling frequency range of the SAR ADC and ΔƩ ADCs.

The solution to this ultra-high-speed ADC challenge is a pipeline ADC that processes multiple samples while still sending data to its output at GSPS speeds.

This article briefly compares ΔƩ, SAR, and pipeline ADCs and then discusses the issues associated with achieving high-speed converter outputs and why pipeline ADCs are an excellent alternative for these high-speed applications. It then introduces two pipeline ADCs from Texas Instruments—one emphasizing precision, the other high speed—and shows how to get started with them.

What is a pipeline ADC?

A pipeline ADC consists of several consecutive stages. The differential structured first stage evaluates the most significant bit (MSB) value and then conditions the signal and passes it on to the next stage for an MSB-1 conversion. Each stage executes its operation concurrently with other stages (Figure 1).

Figure 1: The pipeline topology has multiple stages to implement the conversion of one bit of the multi-bit converter and then conditions the signal and passes the signal to the next stage. (Image source: Texas Instruments)

Figure 1: The pipeline topology has multiple stages to implement the conversion of one bit of the multi-bit converter and then conditions the signal and passes the signal to the next stage. (Image source: Texas Instruments)

In Figure 1, the stages are similar in function and only resolve one or two bits. Each stage has a sample and hold, a low-resolution flash ADC, and a signal conditioning function. The first stage receives the sample and immediately produces an MSB decision. The MSB digital value goes to the first latch (Latch 1). If the MSB decision is one, the stage subtracts the MSB value of charge from the sample. Then the pipeline converter applies a 2x gain multiple to the remaining charge. When a stage completes its operations, it passes the analog difference to the subsequent stages. The beauty of the design with the 2x gain multiple is that Stage 1 through Stage n are fundamentally the same circuitry.

The number of stages often matches the number of ADC bits. The final conversion output combines each stage’s digital results in the output latch. This conversion process results in a data latency of several clock cycles.

Comparison of ΔΣ, SAR and pipeline ADC sampling

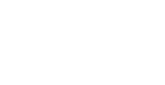

The ΔΣ converter uses an oversampling algorithm to implement finite impulse response (FIR) or infinite impulse response (IIR) digital filters. These filters create signal output latency or delay while acquiring multiple samples, rendering an extremely high resolution as a positive trade-off. As a result, the acquisition time is longer than it is with a SAR or pipeline converter, both of which only sample the signal once for each conversion (Figure 2).

Figure 2: The slowest, highest resolution ΔƩ ADC services lower frequency signals. The moderate speed, medium resolution SAR ADC facilitates general purpose applications. The high-speed, lower resolution pipeline ADC fits into leading-edge high-speed solutions. (Image source: DigiKey)

Figure 2: The slowest, highest resolution ΔƩ ADC services lower frequency signals. The moderate speed, medium resolution SAR ADC facilitates general purpose applications. The high-speed, lower resolution pipeline ADC fits into leading-edge high-speed solutions. (Image source: DigiKey)

The SAR ADC renders a snapshot of the input signal with a defined acquisition point in time. While using charge redistribution techniques, the SAR quickly completes a zero latency conversion. The pipeline converter uses under-sampling technologies to achieve high-speed conversions by engaging charge redistribution techniques as well as delaying the appearance of the results on the output. This conversion algorithm creates data latency.

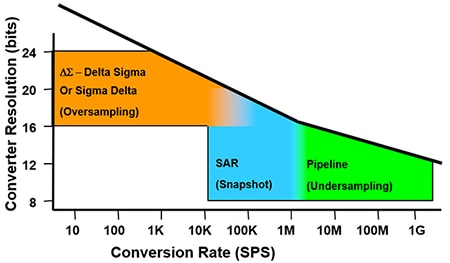

The latency versus conversion speed differs between the SAR, pipeline, and ΔƩ converter (Figure 3).

Figure 3: The ΔƩ oversampling and averaging algorithm creates a delay in the appearance of the final output data word. Since the output of the SAR ADC appears before the next sample acquisition, the latency of the SAR ADC is zero. The data result delay of the pipeline converter creates a non-zero latency. (Image source: DigiKey)

Figure 3: The ΔƩ oversampling and averaging algorithm creates a delay in the appearance of the final output data word. Since the output of the SAR ADC appears before the next sample acquisition, the latency of the SAR ADC is zero. The data result delay of the pipeline converter creates a non-zero latency. (Image source: DigiKey)

In Figure 3, the ΔƩ converter averages multiple samples for each conversion result. The ΔƩ’s averaging filter is usually a FIR or IIR digital filter. This multi-sampling averaging increases the overall conversion time. However, high resolutions are possible, creating a throughput time/accuracy dependency.

The SAR converter’s conversion time encompasses the input signal acquisition time and conversion time. The acquisition time allows for the input signal to settle before the actual moment of signal acquisition occurs. The throughput time is a combination of internal charge redistribution and consecutive serial data output signals, starting with the MSB value.

With a pipeline ADC, the user initiates a sample acquisition with the external input clock’s rising (or falling) edge. The acquired charge for this sample goes to a second stage, while the converter captures the charge equivalent of another input signal, and the second stage ascertains the MSB value. On the following external clock, the second acquired signal goes to the second stage, while the first signal goes to the third stage. During this clock cycle, the determination of the first acquired signal’s MSB-1 and the second acquired signal’s MSB occurs. This process continues with every acquired signal. When an input signal has a complete digital output representation, the converter’s output stage presents a parallel representation of the input signal.

The result of this architecture is that pipeline ADCs are popular for sampling rates from a few megasamples per second to over 1 GSPS. Resolutions range from 8 bits with faster sample rates up to 16 bits with lower rates. These resolutions and sampling rates cover a wide range of applications, including charge coupled device (CCD) imaging, ultrasonic medical imaging, digital receivers, base stations, digital predistortion, and digital video. Some of these applications emphasize precision as well as speed.

Precise pipeline ADCs

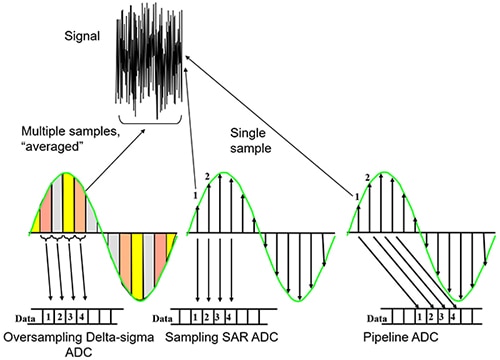

A good example of a precision pipeline ADC is the Texas Instruments ADC16DX370, a 16-bit, 370 MSPS dual-channel pipeline ADC, followed by a back end 7.4 gigabit per second (Gbit/s) JESD204B interface. With a 150 MHz input signal, the ADC16DX370’s signal-to-noise ratio (SNR), spurious free dynamic range (SFDR), and noise spectral density (NSD) are 69.6 decibels at full scale (dBFS), 88 dBFS, and -152.3 dBFS/Hertz, respectively.

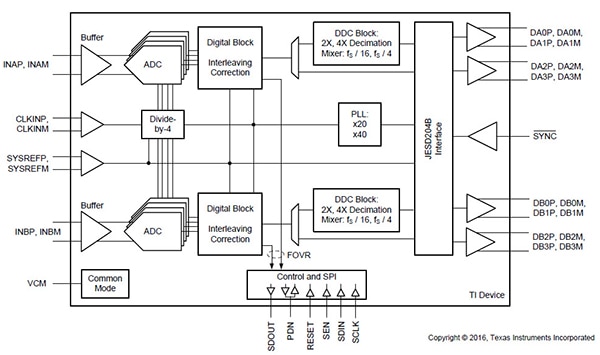

Each ADC has an input buffer and an imbalance correction circuit, as well as the necessary reference voltages with internal drivers. The integrated input buffer eliminates the internal switched sampling capacitor charge and charge kickback noise. This buffer alleviates the driving amplifier, anti-aliasing filter, and impedance matching requirements (Figure 4).

Figure 4: The high-performance 370 MSPS ADC16DX370 is a dual pipeline ADC with an internal reference. It converts analog signals into 16-bit digital words. (Image source: Texas Instruments)

Figure 4: The high-performance 370 MSPS ADC16DX370 is a dual pipeline ADC with an internal reference. It converts analog signals into 16-bit digital words. (Image source: Texas Instruments)

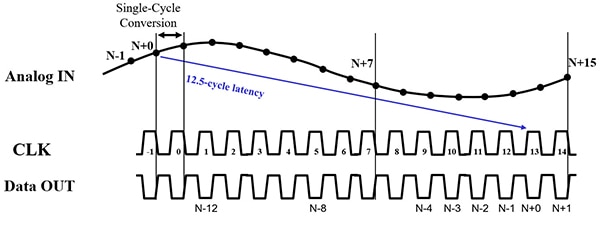

The ADC16DX370 derives the sampling clock from the CLKIN input with a low-noise receiver and clock divider. An input clock divider distributes a high-frequency clock signal throughout the system, and locally divides down at the ADC device to avoid coupling of signals at common intermediate frequencies (IFs) into other parts of the system. The ADC’s core latency is 12.5 clock cycles (Figure 5).

Figure 5: The timing diagram shows the ADC core latency is 12.5 clock cycles. (Image source: DigiKey)

Figure 5: The timing diagram shows the ADC core latency is 12.5 clock cycles. (Image source: DigiKey)

Sampling occurs on the rising edge of the (CLKIN+) − (CLKIN–) differential signal. As a minimum core value, the digital output code is available after 12.5 clock cycles of data latency. The CLKIN input frequency divider factors are 1, 2, 4, or 8.

The ADC16DX370 has differential clock input pins. The internal termination to DC of each pin is a 50 ohm (Ω) resistor for a 100 Ω total internal differential termination. The clock input pins require external AC coupling.

The dual pipeline ADC pc board design is critical to achieving full performance. At least six layers are required to adequately route all signals in and out of the device. Signal routing layers need adjacent solid ground planes to control signal return paths to minimize loop areas, and microstrip and stripline routing needs to be done carefully to control impedances. The use of power planes and adjacent solid ground planes control supply return paths. Also, minimizing the spacing between supply and ground planes increases the distributed decoupling and improves performance.

The target applications for the ADC16DX370 are high IF sampling receivers, multi-carrier base station receivers, and multi-mode and multi-band receivers that complement the higher resolution and 370 MSPS conversion speed. This 16-bit pipeline ADC offers the required SNR (69.6 dBFS) performance for discerning small signals from background noise in an RF heterodyne receiver subsystem, for example.

To help designers evaluate the ADC16DX370, the ADC is supported by the ADC16DX370EVM evaluation board with associated High-Speed Data Converter (HSDC) Pro software. The EVM comes with a mini-USB cable to connect to a PC. TI also provides the TSW16DX370EVM reference design board that can be used to evaluate a receiver IF subsystem solution with over 100 MHz usable bandwidth.

High-speed pipeline ADCs

Where high speed as well as wide dynamic range are priorities, designers can turn to the Texas Instruments ADS54J20, a dual-channel, 12-bit, 1 GSPS ADC. The design of this ADC provides a high SNR of 67.8 dBFS with a noise floor of –157 dBFS/Hz. This ADC is perfect for applications aiming for the highest dynamic range over a wide instantaneous bandwidth (Figure 6).

Figure 6: The ADS54J20 dual pipeline ADC provides an interleaving correction to achieve a noise floor of -157 dBFS/Hz and decimation digital filtering options. (Image source: Texas Instruments)

Figure 6: The ADS54J20 dual pipeline ADC provides an interleaving correction to achieve a noise floor of -157 dBFS/Hz and decimation digital filtering options. (Image source: Texas Instruments)

In Figure 6, the ADS54J20’s interleaving and dither algorithms are used to achieve a clean spectrum with a high SFDR. The device also has various programmable decimation filtering options for systems that need a higher SNR and SFDR over a wide range of frequencies.

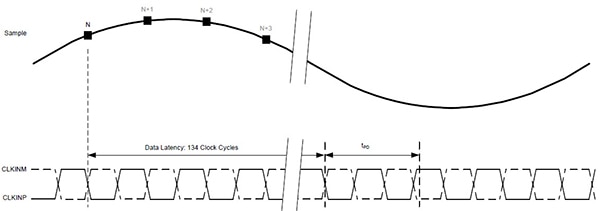

The band-pass decimation filter has a digital mixer and three concatenated FIR filters to create a latency of approximately 134 output clock cycles, plus a logic gates and output buffer propagation delay equaling 4 nanoseconds (ns) (Figure 7).

Figure 7: The timing diagram in the ADC latency is 134 clock cycles plus logic gates and output buffer propagation delay (tPD). (Image source: Texas Instruments)

Figure 7: The timing diagram in the ADC latency is 134 clock cycles plus logic gates and output buffer propagation delay (tPD). (Image source: Texas Instruments)

The digital block, interleaving engine, and the decimation filter (Figure 6, again), in combination with the high-speed sampling 1 gigahertz (GHz) clock frequency contribute to the converter’s latency.

Some of the target applications for the ADS54J20 are radar and antenna arrays, broadband wireless, and cable modem termination system (CMTS) and DOCSIS 3.1 receivers.

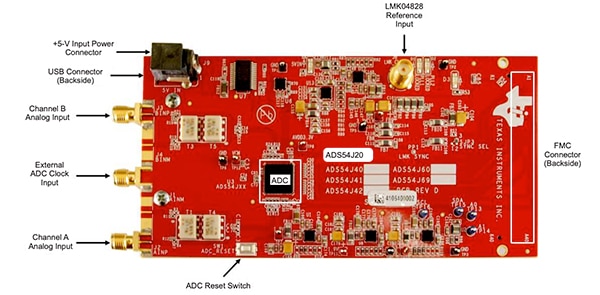

The ADS54J20 is also supported by an evaluation board, in this case the ADS54J20EVM (Figure 8).

Figure 8: The ADS54J20 high-speed ADC is supported by the ADS54J20EVM evaluation board that comes with a mini USB cable and a power supply cable. (Image source: Texas Instruments).

Figure 8: The ADS54J20 high-speed ADC is supported by the ADS54J20EVM evaluation board that comes with a mini USB cable and a power supply cable. (Image source: Texas Instruments).

The ADS54J20EVM is also used in conjunction with HSDC Pro software and comes with a mini USB cable to connect to a PC, as well as a power supply cable.

Conclusion

While SAR and ΔƩ ADCs have their place, the solution to the ultra-high-speed ADC challenge is a pipeline ADC that processes multiple samples while still sending data to its output at hundreds of kilosamples-per-second to gigasample-per-second speeds. Still, not all pipeline ADCs emphasize speed alone. As shown, higher precision can also be achieved.

Regardless of emphasis, pipeline ADCs are an excellent option for high-speed cellular base stations, ultra-high-speed multi-carrier cellular infrastructure base stations, telecommunications, digital predistortion observations, backhaul receivers, and many other applications requiring high-speed conversion.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.