Conceptos fundamentales de los FPGA: ¿Qué son los FPGA y por qué son necesarios?

Colaboración de Editores de DigiKey de América del Norte

2019-11-14

Las soluciones óptimas de procesamiento a menudo son proporcionadas por combinaciones de RISC (computación por conjunto de instrucciones reducidas), CISC (computación por conjunto de instrucciones complejas), procesadores gráficos y FPGA, solo por FPGA, o por FPGA que cuentan con núcleos rígidos de procesadores como parte de su estructura. Sin embargo, muchos diseñadores no están familiarizados con las capacidades de los FPGA, cómo han evolucionado y cómo usarlos. Este artículo, que forma parte de una serie de 5 partes, tratará de los fundamentos de las AGP y presentará ejemplos de soluciones de los principales proveedores. Parte 2, Parte 3, Parte 4 y Parte 5 se centrarán en las familias de dispositivos FPGA y en las herramientas de diseño ofrecidas por Lattice Semiconductor, Microchip, Altera, y Xilinx.

Los diseñadores buscan constantemente formas de diseñar sus sistemas para proporcionar una solución informática óptima que aborde todos los requisitos de sus aplicaciones. En muchas situaciones, esa solución óptima a menudo requiere el uso de arreglos programables de puertas en campo (FPGA), pero muchos diseñadores lamentablemente desconocen las capacidades de estos dispositivos y cómo incorporarlos.

Este artículo describirá brevemente escenarios de diseño que pueden beneficiarse del uso de los FPGA. Luego, describirá los conceptos fundamentales de cómo funcionan antes de presentar algunas soluciones de FPGA y kits de desarrollo interesantes.

¿Por qué usar FPGA?

Hay una amplia gama de aplicaciones informáticas, cada una de las cuales puede funcionar mejor con un enfoque diferente, que incluye microprocesadores (MPU) y microcontroladores (MCU) comerciales, unidades de procesamiento de gráficos (GPU) comerciales, FPGA y dispositivos de sistema en chip (SoC) personalizado. Decidir cuál usar requiere examinar los requisitos y consideraciones de la aplicación.

Por ejemplo, cuando se trabaja con tecnología de vanguardia como las estaciones base 5G, los diseñadores deben tener en cuenta que los estándares y protocolos subyacentes todavía están evolucionando. Esto significa que los diseñadores deben poder responder rápida y eficientemente ante cualquier cambio en las especificaciones que estén fuera de su control.

Asimismo, necesitan la flexibilidad para responder ante los cambios futuros en los estándares y protocolos que ocurren después de que los sistemas se hayan implementado en el campo. Del mismo modo, también es necesario poder responder a errores inesperados en la funcionalidad del sistema o fallas en la seguridad del sistema, modificar la funcionalidad existente o agregar una nueva funcionalidad para extender la vida útil del sistema.

Si bien el SoC proporciona el rendimiento más alto, esta ruta es costosa y requiere mucho tiempo. Además, cualquier algoritmo implementado en la estructura del chip está esencialmente "congelado en silicio". Esta inflexibilidad inherente se convierte en un problema dadas las consideraciones indicadas anteriormente. Para encontrar el punto ideal entre rendimiento y flexibilidad óptimos, se requiere una ruta alternativa. Esa ruta a menudo es proporcionada por los FPGA, combinaciones de microprocesadores/microcontroladores y FPGA, o por FPGA que cuentan con núcleos rígidos de procesadores como parte de su estructura.

¿Qué son los FPGA?

Esta es una pregunta difícil porque los FPGA son muchas cosas para muchas personas. Además, existen muchos tipos diferentes de FPGA, cada uno con diferentes combinaciones de capacidades y funciones.

En el centro de cualquier FPGA, el aspecto definitorio de “FPGA-dom”, por así decirlo, es su estructura programable, que se presenta como un arreglo de bloques lógicos programables (Figura 1a). Cada uno de estos bloques lógicos contiene una colección de elementos, incluida una tabla de consulta (LUT), un multiplexor y un registro; todos se pueden configurar (programar) para que funcionen según sea necesario (Figura 2).

Figura 1: Los FPGA más simples contienen solo estructura programable y GPIOS configurables (a), diferentes arquitecturas aumentan esta estructura básica con bloques SRAM (memoria estática de acceso aleatorio), PLL (circuitos de sincronización de fase) y administradores de reloj (b), bloques DSP (procesador de señal digital) e interfaces SERDES (c), y núcleos y periféricos rígidos del procesador (d). (Fuente de la imagen: Max Maxfield)

Figura 1: Los FPGA más simples contienen solo estructura programable y GPIOS configurables (a), diferentes arquitecturas aumentan esta estructura básica con bloques SRAM (memoria estática de acceso aleatorio), PLL (circuitos de sincronización de fase) y administradores de reloj (b), bloques DSP (procesador de señal digital) e interfaces SERDES (c), y núcleos y periféricos rígidos del procesador (d). (Fuente de la imagen: Max Maxfield)

Figura 2: Cada bloque lógico programable contiene una colección de elementos, que incluyen una tabla de consulta, un multiplexor y un registro; todos se pueden configurar (programar) para que funcionen según sea necesario. (Fuente de la imagen: Max Maxfield)

Figura 2: Cada bloque lógico programable contiene una colección de elementos, que incluyen una tabla de consulta, un multiplexor y un registro; todos se pueden configurar (programar) para que funcionen según sea necesario. (Fuente de la imagen: Max Maxfield)

Muchos FPGA utilizan LUT de 4 entradas que se pueden configurar para implementar cualquier función lógica de 4 entradas. Con el fin de admitir mejor las amplias rutas de datos utilizadas en algunas aplicaciones, algunos FPGA ofrecen LUT de 6, 7 o incluso 8 entradas. La salida de la LUT está conectada directamente a una de las salidas del bloque lógico y a una de las entradas del multiplexor. La otra entrada al multiplexor está directamente conectada a una entrada de bloque lógico (e). El multiplexor se puede configurar para que seleccione cualquiera de estas entradas.

La salida del multiplexor alimenta la entrada de registro. Cada registro se puede configurar para que funcione como un biestable activado por flanco o un pestillo sensible al nivel (dicho esto, no se recomienda el uso de lógica asincrónica en forma de pestillos dentro de los FPGA). El reloj de cada registro (o la activación) se puede configurar para estar alto activo o bajo activo; de manera similar, el nivel activo de las entradas de set/reset también se puede configurar.

Estos bloques lógicos pueden considerarse como "islas de lógica programable" que flotan en un "mar de interconexión programable". La interconexión se puede configurar para conectar cualquier salida de cualquier bloque lógico a cualquier entrada de otro bloque lógico. De manera similar, las entradas principales al FPGA se pueden conectar a las entradas de cualquier bloque lógico, y las salidas de cualquier bloque lógico se pueden usar para controlar las salidas principales del dispositivo.

Las entradas y salidas principales de uso general (GPIO) se presentan en bancos (grupos), donde cada banco se puede configurar para admitir un estándar de interfaz diferente, como LVCMOS (semiconductor complementario de óxido metálico de bajo voltaje), LVDS (tecnología de señal diferencial de bajo voltaje), LVTTL (lógica de transistor a transistor de bajo voltaje), HSTL (lógica de transceptor de alta velocidad) o SSTL (lógica terminada de la serie stub). Además, la impedancia de las entradas se puede configurar, al igual que la velocidad de respuesta de las salidas.

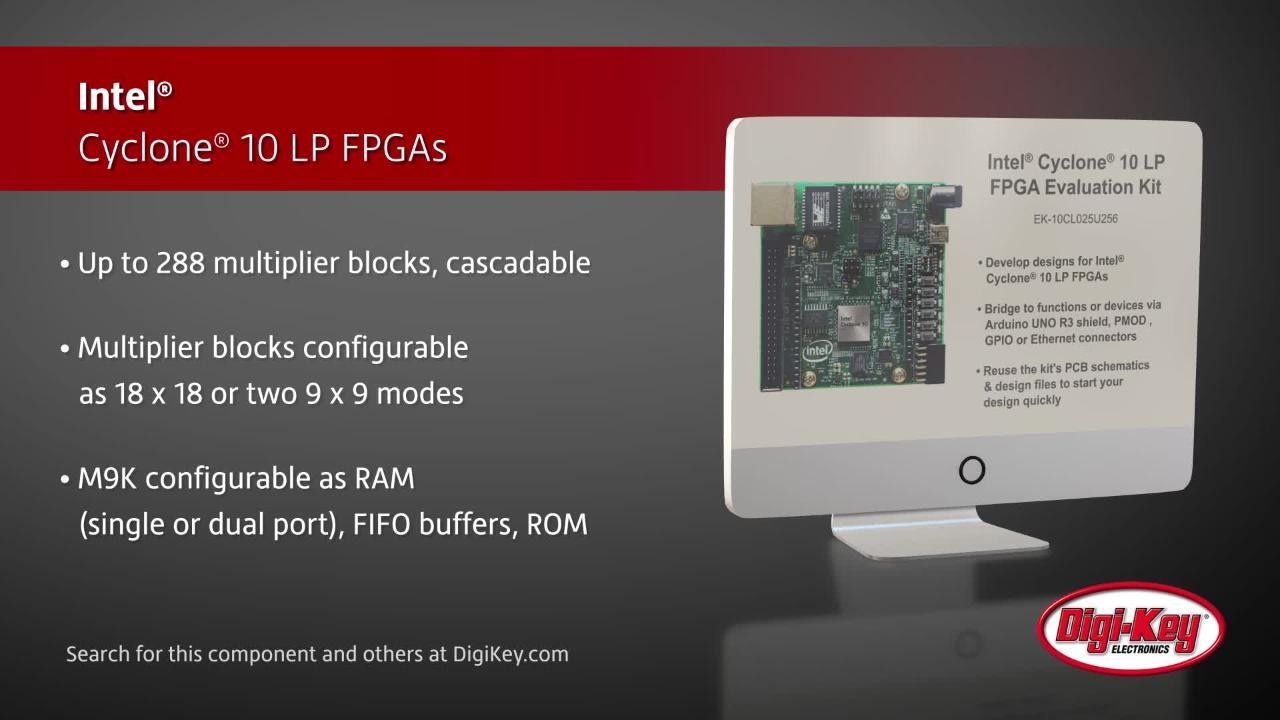

El siguiente paso en la estructura de los FPGA incluye elementos como bloques de SRAM, llamados RAM de bloque (BRAM), circuitos de sincronización de fase (PLL) y administradores de reloj (Figura 1b). También se pueden agregar bloques de procesamiento de señal digital (DSP), también llamados “cortes de DSP” (DSP slices). Estos contienen multiplicadores configurables y un sumador configurable que les permite realizar operaciones de multiplicación-acumulación (MAC) (Figura 1c).

Otra característica común de los FPGA son los bloques SERDES de alta velocidad, que pueden soportar interfaces gigabit seriales. Es importante tener en cuenta que no todos los FPGA poseen todas las características mencionadas anteriormente. Diferentes FPGA ofrecen diferentes colecciones de características dirigidas a diferentes mercados y aplicaciones.

La estructura programable en un FPGA puede usarse para implementar cualquier función lógica o conjunto de funciones deseadas, hasta el núcleo de un procesador, o incluso múltiples núcleos. Si estos núcleos se implementan en una estructura programable, se denominan "núcleos flexibles". En comparación, algunos FPGA comúnmente denominados FPGA de SoC, contienen uno o más procesadores de "núcleo rígido", que se implementan directamente en el silicio (Figura 1d). Estos núcleos rígidos del procesador pueden incluir unidades de coma flotante (FPU) y caché de nivel 1 y 2.

Del mismo modo, las funciones de la interfaz periférica como CAN, I2C, SPI, UART y USB se pueden implementar como núcleos flexibles en la estructura programable, pero muchos FPGA los incluyen como núcleos rígidos en el silicio. Las comunicaciones entre los núcleos del procesador, las funciones de la interfaz y la estructura programable generalmente se realizan mediante buses de alta velocidad como AMBA y AXI.

Los primeros FPGA, que fueron presentados al mercado por Xilinx en 1985, contenían solo una matriz de bloques lógicos programables de 8 x 8 (sin bloques RAM, bloques DSP, etc.). En comparación, los FPGA de gama alta actuales pueden contener cientos de miles de bloques lógicos, miles de bloques DSP y megabits de RAM. En total, pueden contener miles de millones de transistores que equivalen a decenas de millones de puertas equivalentes (por ejemplo, puertas NAND de 2 entradas).

Tecnologías alternativas de configuración

La forma en que se determinan las funciones de los bloques lógicos y el enrutamiento de la interconexión es mediante celdas de configuración, que pueden visualizarse como interruptores 0/1 (apagado/encendido). Estas celdas también se usan para configurar el estándar de interfaz de GPIO, la impedancia de entrada, la velocidad de respuesta de salida, etc. Dependiendo del FPGA, estas celdas de configuración pueden implementarse usando una de tres tecnologías:

- Antifusible: Estas celdas de configuración son programables una sola vez (OTP), lo que significa que una vez que el dispositivo ha sido programado no hay vuelta atrás. Estos dispositivos tienden a estar limitados a aplicaciones espaciales y de alta seguridad. Como se venden en pequeñas cantidades, su precio es alto y son una opción costosa de diseño.

- Flash: Al igual que las celdas de configuración basadas en antifusibles, las celdas basadas en flash son no volátiles. A diferencia de las celdas de antifusibles, las celdas de flash pueden reprogramarse según sea necesario. Las celdas de configuración flash son tolerantes a la radiación, lo que hace que estos dispositivos sean adecuados para aplicaciones espaciales (aunque con modificaciones en sus capas y paquetes de metalización superiores).

- SRAM: En este caso, los datos de configuración se almacenan en una memoria externa desde donde se cargan cada vez que se activa el FPGA (o según se recomiende en el caso de escenarios de configuración dinámica).

Las ventajas de los FPGA cuyas celdas de configuración están basadas en antifusibles o flash es que "se activan instantáneamente" y consumen poca energía. Una desventaja de estas tecnologías es que requieren pasos de procesamiento adicionales además del proceso de CMOS (semiconductor complementario de óxido metálico) subyacente utilizado para crear el resto del chip.

La ventaja de los FPGA cuyas celdas de configuración se basan en la tecnología SRAM es que se fabrican utilizando el mismo proceso de CMOS que el resto del chip, y ofrecen un mayor rendimiento porque generalmente están una o dos generaciones por delante de las tecnologías antifusible y flash. Las principales desventajas son que las celdas de configuración SRAM consumen más energía que sus contrapartes antifusible y flash (en el mismo nodo tecnológico), y son susceptibles a alteraciones por evento único (SEU) causadas por la radiación.

Durante mucho tiempo, este último punto implicó que los FPGA basados en SRAM se consideraban inadecuados para aplicaciones aeroespaciales y espaciales. Más recientemente, se han empleado estrategias especiales de mitigación, con el resultado de que los FPGA basados en SRAM se encuentran en sistemas como el Mars Curiosity Rover, junto con sus primos basados en flash.

Usar FPGA ofrece flexibilidad

Los FPGA se utilizan para muchas aplicaciones diversas. Son particularmente útiles para implementar funciones de interfaz inteligente, control de motores, aceleración algorítmica y computación de alto rendimiento (HPC), procesamiento de imágenes y videos, visión artificial, inteligencia artificial (AI), aprendizaje automático (ML), aprendizaje profundo (DL), radares, conformación de haces, estaciones base y comunicaciones.

Un ejemplo simple es proporcionar una interfaz inteligente entre otros dispositivos que utilizan diferentes estándares de interfaz o protocolos de comunicación. Considere un sistema existente que contiene un procesador de aplicaciones conectado al sensor de una cámara y un dispositivo de visualización que utiliza interfaces heredadas (Figura 3a).

Figura 3: Se puede usar un FPGA para proporcionar una interfaz inteligente entre otros dispositivos que usan diferentes estándares de interfaz o protocolos de comunicación, lo que extiende así la vida de los diseños existentes basados en dispositivos heredados. (Fuente de la imagen: Max Maxfield)

Figura 3: Se puede usar un FPGA para proporcionar una interfaz inteligente entre otros dispositivos que usan diferentes estándares de interfaz o protocolos de comunicación, lo que extiende así la vida de los diseños existentes basados en dispositivos heredados. (Fuente de la imagen: Max Maxfield)

Ahora, supongamos que los creadores del sistema desean actualizar el sensor de la cámara y el dispositivo de visualización a algo más moderno que sea más liviano, más barato y consuma menos energía. El único problema es que uno o ambos de estos nuevos periféricos pueden usar un estándar de interfaz moderno que no es compatible con el procesador de aplicación (AP) original. Alternativamente, pueden admitir un protocolo de comunicaciones completamente diferente, como la interfaz de procesador de la industria móvil (MIPI). En este caso, el uso de un FPGA con su capacidad de soportar múltiples estándares de E/S, junto con algunos núcleos flexibles IP de MIPI, proporcionará una ruta de actualización rápida, de bajo costo y sin riesgos (Figura 3b).

Como otro ejemplo de aplicación, considere alguna tarea de computación intensiva, como realizar el procesamiento de señales requerido para implementar un sistema de radar, o la conformación de haces en una estación base de comunicaciones. Los procesadores convencionales con sus arquitecturas von Neumann o Harvard son adecuados para ciertas tareas, pero son menos adecuados para aquellas que requieren que la misma secuencia de operaciones se realice repetidamente. Esto se debe a que un solo núcleo del procesador que usa un solo hilo de ejecución solo puede ejecutar una instrucción a la vez (Figura 4a).

Figura 4: A diferencia de los microprocesadores en los que solo se puede ejecutar una sola instrucción a la vez (secuencialmente), varios bloques funcionales en un FPGA pueden ejecutarse al mismo tiempo (simultáneamente); además, los FPGA pueden implementar algoritmos apropiados de forma paralela y masiva. (Fuente de la imagen: Max Maxfield)

Figura 4: A diferencia de los microprocesadores en los que solo se puede ejecutar una sola instrucción a la vez (secuencialmente), varios bloques funcionales en un FPGA pueden ejecutarse al mismo tiempo (simultáneamente); además, los FPGA pueden implementar algoritmos apropiados de forma paralela y masiva. (Fuente de la imagen: Max Maxfield)

En comparación, se pueden ejecutar múltiples funciones simultáneamente en el FPGA, lo cual permite canalizar una serie de operaciones y a su vez, permite una tasa de producción mucho mayor. De manera similar, en lugar de realizar la misma operación, digamos 1,000 veces adicionales en 1,000 pares de valores de datos con el procesador, los mismos cálculos podrían realizarse de una manera paralela y masiva en un solo ciclo de reloj en el FPGA al instanciar 1,000 sumadores en la estructura programable (Figura 4b).

¿Quién hace los FPGA?

Este es un paisaje en constante evolución. Los dos principales fabricantes de dispositivos realmente de alta gama con la mayor capacidad y rendimiento son Intel (que adquirió Altera) y Xilinx.

Las ofertas de Intel y Xilinx abarcan los rangos desde FPGA de gama baja hasta FPGA de SoC de gama alta. Otro proveedor que se centra casi exclusivamente en los FPGAs es Lattice Semiconductor, que apunta a aplicaciones de gama baja y media. Por último, pero no menos importante, Microchip Technology (a través de sus adquisiciones de Actel, Atmel, y Microsemi) ahora tiene múltiples familias de FPGA pequeñas y medianas y miembros de gama baja de la categoría de FPGA de SoC.

Elegir el mejor dispositivo para la tarea en cuestión puede ser complicado porque existen muchas familias, y cada una de ellas ofrece diferentes recursos, rendimientos, capacidades y estilos de presentación. Aquí hay algunos ejemplos: Dispositivos Intel; dispositivos Lattice Semiconductory dispositivos Xilinx.

¿Cómo diseñar con FPGA?

La forma tradicional de diseñar FPGA es que los ingenieros utilicen un lenguaje de descripción de hardware como Verilog o VHDL para capturar la intención del diseño. Estas descripciones se pueden simular primero para verificar que funcionen según sea necesario, después de lo cual se pasan a una herramienta de síntesis que genera el archivo de configuración utilizado para configurar (programar) el FPGA.

Cada proveedor de FPGA tiene su propia cadena de herramientas desarrollada internamente u ofrece una versión personalizada de una herramienta de un proveedor especializado. En cualquier caso, se puede acceder a esas herramientas desde los sitios web de los proveedores de FPGA. Además, puede haber versiones gratuitas o de bajo costo de los conjuntos de herramientas completos.

Para que los desarrolladores de software tengan acceso a los FPGA, algunos de los proveedores de FPGA ahora ofrecen herramientas de síntesis de alto nivel (HLS). Estas herramientas interpretan una descripción algorítmica del comportamiento deseado capturado en un alto nivel de abstracción en C, C++ u OpenCL, y generan la entrada para alimentar el motor de síntesis de nivel inferior.

Para los diseñadores que buscan comenzar, existen muchas placas de desarrollo y evaluación disponibles, cada una de las cuales ofrece diferentes capacidades y características. Tres ejemplos son el kit de desarrollo DFR0600 de DFRobot que presenta un FPGA de SoC Zynq-7000 de Xilinx, el DE10 Nano de Terasic Inc. que cuenta con un FPGA de SoC Cyclone V de Intel, y la placa de evaluación ICE40HX1K-STICK-EVN que presenta un FPGA iCE40 de baja potencia de Lattice Semiconductor.

Los diseñadores que planean usar una tarjeta dependiente PCIe basada en FPGA para acelerar las aplicaciones que se ejecutan en una placa base X86 pueden desear mirar algo como una de las tarjetas dependientes PCIe Alveo, también de Xilinx.

Conclusión

Las soluciones de diseño óptimas a menudo son proporcionadas por FPGA, combinaciones de procesadores y FPGA, o por FPGA que cuentan con núcleos rígidos de procesadores como parte de su estructura.

Los FPGA han evolucionado rápidamente a lo largo de los años y pueden abordar muchos requisitos de diseño en términos de flexibilidad, velocidad de procesamiento y potencia, lo que los hace útiles para una amplia gama de aplicaciones.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.