Fundamentos de las FPGA - Parte 5: Cómo empezar con las FPGA de Intel (Altera)

Colaboración de Editores de DigiKey de América del Norte

2020-05-07

Nota del editor: Las soluciones de procesamiento óptimas suelen ser proporcionadas por combinaciones de RISC, CISC, procesadores gráficos y FPGA; FPGA por sí mismas; o por FPGA que cuentan con núcleos de procesador duro como parte de su tejido. Sin embargo, muchos diseñadores no están familiarizados con las capacidades de los FPGA, cómo han evolucionado y cómo usarlos.La parte 1 de esta serie de varias partes proporciona una introducción de alto nivel a las FPGA; La parte 2 se centra en las ofertas de FPGA de Lattice Semiconductor; y la parte 3 se centra en las familias de dispositivos FPGA y en las herramientas de diseño de Microchip Technology (de su filial Microsemi Corporation). La parte 4 ahonda en los componentes y herramientas de Xilinx. Aquí, la Parte 5 considera las ofertas de Altera, que fue adquirida por Intel y ahora forma parte del grupo Programmable Solutions Group de Intel (para el resto de este documento, se utiliza el nombre Intel).

Como se expuso en la primera parte, los conjuntos de puertas programables en el terreno (FPGA) tienen muchas características que los convierten en un activo informático inestimable, ya sea utilizados de forma autónoma o en una arquitectura heterogénea, pero muchos diseñadores no están familiarizados con las FPGA ni con la forma de incorporar estos dispositivos en sus diseños. Una forma de superar este impedimento es mirar más profundamente las arquitecturas FPGA y las herramientas asociadas de los principales proveedores.

Descripción general de las opciones de FPGA de alto nivel

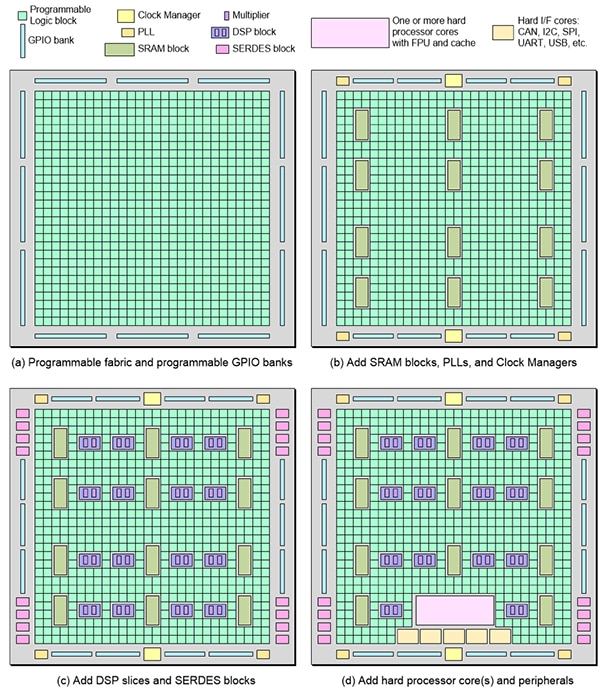

Existen muchos tipos diferentes de FPGA en el mercado, cada uno con diferentes combinaciones de capacidades y funciones. En el corazón de cualquier FPGA está su tejido programable. Esto se presenta como un conjunto de bloques lógicos programables, también conocidos como elementos lógicos (LE) (Figura 1(a)). El siguiente paso en el tejido de la FPGA es incluir cosas como bloques de SRAM, llamados bloque RAM (BRAM), bucles de bloqueo de fase (PLL), y administradores de reloj (Figura 1(b)). También se pueden añadir bloques de procesamiento de señales digitales (DSP) (llamados rebanadas DSP) y bloques de serializador/deserializador de alta velocidad (SERDES) (Figura 1(c)).

Figura 1: Los FPGA más simples contienen sólo tejido programable e IO de propósito general configurable (GPIO) (a); las diferentes arquitecturas aumentan este tejido fundamental con bloques SRAM, PLL y gestores de reloj (b); bloques DSP e interfaces SERDES (c); y núcleos de procesador duro y periféricos (d). (Fuente de la imagen: Max Maxfield)

Figura 1: Los FPGA más simples contienen sólo tejido programable e IO de propósito general configurable (GPIO) (a); las diferentes arquitecturas aumentan este tejido fundamental con bloques SRAM, PLL y gestores de reloj (b); bloques DSP e interfaces SERDES (c); y núcleos de procesador duro y periféricos (d). (Fuente de la imagen: Max Maxfield)

Las funciones de la interfaz periférica como CAN, I2C, SPI, UART y USB se pueden implementar como núcleos flexibles en la estructura programable, pero muchos FPGA las incluyen como núcleos rígidos en el silicio. Del mismo modo, los microprocesadores pueden implementarse como núcleos flexibles en la estructura programable o como núcleos rígidos en el silicio (Figura 1(d)). Los FPGA con núcleos de procesador duro se denominan FPGA de sistema en chip (SoC). Diferentes FPGA ofrecen distintos conjuntos de funciones, características y capacidades dirigidas a diferentes mercados y aplicaciones.

Hay varios proveedores de FPGA, incluyendo Intel (que adquirió Altera), Efinix, Lattice Semiconductor, Microchip Technology (que adquirió Atmel y Microsemi), y Xilinx.

Todos estos proveedores ofrecen múltiples familias de FPGA; algunos ofrecen FPGA de SoC, algunos ofrecen dispositivos dirigidos a aplicaciones de inteligencia artificial (AI) y aprendizaje automático (ML), y algunos ofrecen dispositivos tolerantes a la radiación para aplicaciones de espacio. Elegir el mejor dispositivo para la tarea en cuestión puede ser complicado porque existen muchas familias y cada una de ellas ofrece diferentes recursos.

Presentación de las FPGA de Intel y las FPGA de SoC

El rendimiento y las capacidades de la oferta de dispositivos programables de Intel van de modestos a extremadamente altos, desde las FPGA tradicionales hasta las FPGA de SoC (es decir, dispositivos que combinan el tejido programable de las FPGA con uno o más núcleos de procesador endurecidos).

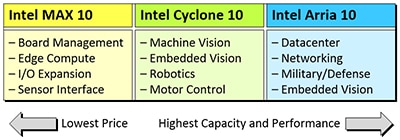

Intel tiene cinco familias de FPGA activas en su actual cartera de productos, entre ellas la Max 10, Cyclone 10 y Arria 10 (Figura 2). Intel también tiene el Stratix 10 de gama alta y sus nuevos y avanzados dispositivos Agilex.

Figura 2: Aplicaciones y mercados objetivo para tres de las cinco familias de FPGA de Intel, desde el menor costo (Max 10) hasta la mayor capacidad y rendimiento (Arria 10), que van desde la gestión de placas y la expansión de E/S hasta la visión integrada y la defensa/militar. El Stratix 10 y los nuevos dispositivos Agilex amplían aún más el rendimiento. (Fuente de la imagen: Max Maxfield)

Figura 2: Aplicaciones y mercados objetivo para tres de las cinco familias de FPGA de Intel, desde el menor costo (Max 10) hasta la mayor capacidad y rendimiento (Arria 10), que van desde la gestión de placas y la expansión de E/S hasta la visión integrada y la defensa/militar. El Stratix 10 y los nuevos dispositivos Agilex amplían aún más el rendimiento. (Fuente de la imagen: Max Maxfield)

Las FPGA Intel Max 10 incorporan memoria flash NOR en el chip para mantener la configuración de la FPGA. Las otras familias de productos tienen células de configuración basadas en SRAM y cargan sus configuraciones en el encendido desde un dispositivo de memoria externa integrada o desde cualquier otra parte del sistema (por ejemplo, bajo el control de un procesador externo). Excepto la familia MAX 10, todas las demás familias de FPGA de Intel están disponibles como FPGA o como FPGA SoC con sistemas de microprocesadores endurecidos integrados.

Las características integradas de las FPGA MAX 10 incluyen convertidores analógico-digitales (ADC) y flash de doble configuración, que proporciona la capacidad de almacenar y cambiar dinámicamente entre dos imágenes en un solo chip. Las FPGA MAX 10 también cuentan con soporte de procesador integrado de núcleo blando Nios II, bloques DSP y controladores de memoria de doble velocidad de datos 3 (DDR3).

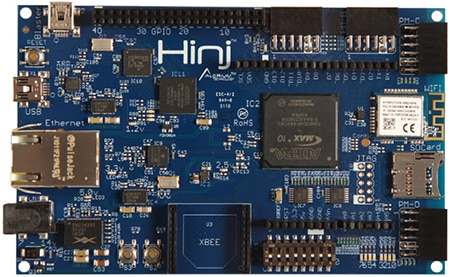

Un dispositivo representativo de la cartera del MAX 10 sería el 10M16SCU169I7P con 16.000 elementos lógicos/células, 562.176 bits de RAM en total y 130 entradas/salidas (E/S). Una placa de evaluación adecuada para el MAX 10 es la de Intel EK-10M08E144. Otro es el HINJKIT, un kit de desarrollo del centro de sensores FPGA IoT de Alorium Technology, LLC (Figura 3). El HINJKIT es de particular interés porque su FPGA MAX 10 incluye el microcontrolador de 8 bits compatible con AVR de Alorium Technology, lo que permite que el HINJKIT sea utilizado con el IDE de Arduino. La placa también proporciona un alto nivel de flexibilidad de interfaz para placas portadoras de IoT de terceros, módulos y accesorios.

Figura 3: El HINJKIT es una plataforma de desarrollo FPGA MAX 10 de Alorium que proporciona un alto nivel de flexibilidad de interfaz para placas portadoras de IoT de terceros, módulos y accesorios. (Fuente de la imagen: Alorium Technology)

Figura 3: El HINJKIT es una plataforma de desarrollo FPGA MAX 10 de Alorium que proporciona un alto nivel de flexibilidad de interfaz para placas portadoras de IoT de terceros, módulos y accesorios. (Fuente de la imagen: Alorium Technology)

Las FPGA de Intel Cyclone 10 GX proporcionan funciones basadas en transceptores de 12.5 gigabytes (Gbytes), 1.4 gigabits por segundo (Gbit/s) de señalización diferencial de bajo voltaje (LVDS) y una interfaz SDRAM DDR3 de hasta 72 bits de ancho para velocidades de datos de hasta 1,866 megabits por segundo (Mbits/s). Las FPGA Cyclone 10 GX están optimizadas para aplicaciones de alto rendimiento de ancho de banda como la visión artificial, la conectividad de video y las cámaras de visión inteligente.

En comparación, las FPGACyclone 10 LP están optimizadas para aplicaciones de baja potencia estática y bajo coste como la expansión de E/S, la fusión de sensores, el control de motores/movimientos, el puente entre chips y el control. Tanto la familia de dispositivos GX como la LP soportan la migración vertical, permitiendo a los diseñadores comenzar los diseños con un dispositivo y migrar a densidades adyacentes en una fecha posterior.

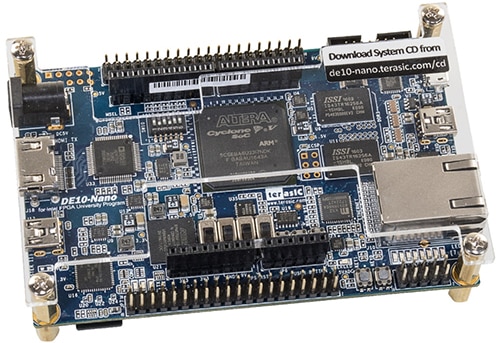

Un miembro representativo de la cartera Cyclone 10 sería el 10CL006YU256A7G con 6,272 elementos lógicos/células, 276,480 bits totales de RAM, y 176 E/S. Hay una variedad de placas y módulos de desarrollo y evaluación relacionados disponibles, incluyendo el Kit SoC P0496 DE10-NANO Cyclone V SE (Figura 4), la placa de evaluación P0553 TSoM Cyclone V SE (de nuevo basado en la FPGA de SoC Cyclone V) y la placa de evaluación FPGA P0581 TSoM Cyclone V SE, todos de Terasic Inc. (Nótese que la FPGA Cyclone V que aparece en estas placas es una generación anterior de la familia Cyclone 10).

Figura 4: El kit de desarrollo P0496 DE10-NANO de bajo costo presenta una plataforma de diseño de hardware resistente que permite a los usuarios experimentar y evaluar las FPGA Cyclone. (Fuente de la imagen: Terasic Inc.)

Figura 4: El kit de desarrollo P0496 DE10-NANO de bajo costo presenta una plataforma de diseño de hardware resistente que permite a los usuarios experimentar y evaluar las FPGA Cyclone. (Fuente de la imagen: Terasic Inc.)

Basados en la tecnología de proceso de 20 nanómetros (nm) de TSMC, los dispositivos Arria 10 combinan un doble núcleo Arm Cortex-A9 MPCore Hard Processor System (HPS) con un tejido programable que incluye bloques DSP de punto flotante endurecidos. Los dispositivos Arria 10 también cuentan con transceptores de alta velocidad incorporados, controladores de memoria dura y controladores de propiedad intelectual de protocolos (IP), todo en un único paquete altamente integrado.

Un dispositivo representativo de la cartera Arria 10 sería el 10AX022C4U19E3SG, con 220,000 elementos lógicos/células, 13,752,320 bits totales de RAM, y 240 E/S. Para desarrollar con esta FPGA, una plataforma adecuada es la placa de evaluación FPGADK-DEV-10AX115S-A Arria 10 GX de Intel (Figura 5). Esta placa permite a los diseñadores desarrollar y probar diseños PCI Express (PCIe) 3.0 basados en Arria 10; desarrollar y probar subsistemas de memoria consistentes en memorias DDR4, DDR3, QDR IV y RLDRAM III; y desarrollar diseños modulares y escalables utilizando los conectores de la tarjeta mezzanine FPGA (FMC) para interconectarse con una tarjeta mezzanine FMC proporcionada por socios de Intel.

Figura 5: El kit de desarrollo FPGA DK-DEV-10AX115S-A Arria 10 GX ofrece un completo entorno de diseño que incluye todo el hardware y el software necesarios para desarrollar y probar diseños basados en PCIe, subsistemas de memoria y sistemas basados en tarjetas FMC. (Fuente de la imagen: Intel)

Figura 5: El kit de desarrollo FPGA DK-DEV-10AX115S-A Arria 10 GX ofrece un completo entorno de diseño que incluye todo el hardware y el software necesarios para desarrollar y probar diseños basados en PCIe, subsistemas de memoria y sistemas basados en tarjetas FMC. (Fuente de la imagen: Intel)

Las FPGA Stratix 10 de Intel y las FPGA SoC presentan la arquitectura Intel Hyperflex FPGA. Las FPGA de esta línea de dispositivos satisfacen las necesidades de los sistemas de alto rendimiento con hasta 10 TFLOPS de rendimiento en punto flotante y soporte de transceptores de 28.3 Gbits/s (GX) a 57.8 Gbits/s, estos últimos en hasta 144 carriles de transceptores para satisfacer las demandas de ancho de banda de las comunicaciones de 5G, la computación en nube, la virtualización de redes y las redes de transporte óptico. Una variante incluye una interfaz PCIe Gen4 con una configuración de hasta x16 a 16 transferencias de giga por segundo (GT/s) y un nuevo controlador de memoria para soportar la memoria persistente Intel Optane DC seleccionada.

Para apoyar el desarrollo con la línea Stratix 10, está la placa de evaluación FPGA DK-DEV-1SGX-L-A Stratix 10 GX de Intel (Figura 6). Esta placa permite a los diseñadores desarrollar y probar diseños PCI Express (PCIe) 3.0 basados en Stratix 10; desarrollar y probar subsistemas de memoria consistentes en memorias DDR4, DDR3, QDR IV y RLDRAM III; y desarrollar diseños modulares y escalables utilizando los conectores de la tarjeta mezzanine FPGA (FMC) para interconectarse con una tarjeta mezzanine FMC, también proporcionada por socios de Intel.

Figura 6: La tarjeta de evaluación FPGA DK-DEV-1SGX-L-A Stratix 10 GX ofrece un entorno de diseño completo que incluye todo el hardware y el software necesarios para desarrollar y probar diseños basados en PCIe, subsistemas de memoria y sistemas basados en tarjetas FMC. (Fuente de la imagen: Intel)

Figura 6: La tarjeta de evaluación FPGA DK-DEV-1SGX-L-A Stratix 10 GX ofrece un entorno de diseño completo que incluye todo el hardware y el software necesarios para desarrollar y probar diseños basados en PCIe, subsistemas de memoria y sistemas basados en tarjetas FMC. (Fuente de la imagen: Intel)

Diseño y desarrollo con las FPGA de Intel y las FPGA de SoCs

En la primera parte de esta serie sobre las FPGA, observamos que la forma tradicional de diseñar estos dispositivos es que los ingenieros utilicen un lenguaje de descripción de hardware (HDL), como Verilog o VHDL para captar la intención del diseño a un nivel de abstracción conocido como nivel de transferencia de registros (RTL). Estas descripciones RTL pueden ser simuladas primero para verificar que funcionan como se requiere, después de lo cual se pasan a una herramienta de síntesis que genera el archivo de configuración usado para configurar (programar) la FPGA.

El siguiente paso en la abstracción es capturar la intención del diseño usando un lenguaje de programación como C/C++, o una implementación especial como SystemC, que es un conjunto de clases y macros de C++ que proporcionan una interfaz de simulación dirigida por eventos. Estos facilitan la simulación de procesos concurrentes, cada uno de los cuales se describe utilizando una sintaxis sencilla de C++. Tales descripciones pueden ser analizadas y perfiladas ejecutándolas como programas regulares, después de lo cual se pasan a un motor de síntesis de alto nivel (HLS), que produce RTL que se alimenta en el motor de síntesis regular.

En un nivel conceptualmente más alto de abstracción se encuentra el Open CL (Open Computing Language), que es un marco para escribir programas que se ejecutan a través de plataformas heterogéneas. Además de las FPGA, estas plataformas incluyen unidades centrales de procesamiento (CPU), unidades de procesamiento de gráficos (GPU), procesadores de señales digitales (DSP) y otros procesadores o aceleradores de hardware. OpenCL especifica los lenguajes de programación (basados en C99 y C++11) para programar estos dispositivos, junto con interfaces de programación de aplicaciones (API) para controlar la plataforma y ejecutar programas en los dispositivos de computación.

En el caso de las FPGA de Intel y las FPGA de SoC, los usuarios desarrollan diseños para todas las familias de productos utilizando el software de diseño Quartus Prime de Intel. Este software está disponible en tres versiones: Quartus Prime Pro Edition, Quartus Prime Standard Edition y Quartus Prime Lite Edition. Las ediciones Pro y Standard requieren licencias pagadas, mientras que la edición Lite puede ser descargada gratuitamente.

La edición Pro está optimizada para soportar las características avanzadas de las FPGA y SoC de próxima generación con las familias de dispositivos Agilex, Stratix 10, Arria 10 y Cyclone 10 GX; la edición Standard incluye un amplio soporte para las familias de dispositivos anteriores, además de la familia de dispositivos Cyclone 10 LP; y la edición Lite, que está disponible como descarga gratuita sin necesidad de un archivo de licencia, proporciona un punto de entrada ideal para las familias de dispositivos de gran volumen.

Intel ofrece una enorme gama de herramientas y recursos de diseño adicionales, incluyendo Intel DSP Builder, Intel High Level Synthesis (HLS) Compiler, y Intel FPGA SDK para OpenCL.

También es útil la Distribución de Intel del OpenVINO Toolkit, que permite a los desarrolladores crear aplicaciones de inteligencia artificial (IA), visión por computador, audio, habla y lenguaje, permitiendo la inferencia de aprendizaje profundo desde el borde hasta la nube. Además de las FPGA, este juego de herramientas soporta la ejecución heterogénea a través de la arquitectura de Intel y los aceleradores AI - CPU, iGPU, Unidad de Procesamiento de Visión Movidius (VPU) de Intel y Acelerador Neural (GNA) de Intel Gaussian - utilizando una API común. Este kit de herramientas está respaldado por el kitOpenVINO Starter Kit basado en la FPGA Cyclone V GT.

Conclusión

Las soluciones óptimas de diseño de procesamiento a menudo son proporcionadas por combinaciones de procesadores y FPGA, por FPGA por sí solos o por FPGA que cuentan con núcleos de procesadores duros como parte de su tejido. Como tecnología, las FPGA han evolucionado rápidamente a lo largo de los años y son capaces de hacer frente a muchos requisitos de diseño en términos de flexibilidad, velocidad de procesamiento y potencia, lo que las hace muy útiles para una amplia gama de aplicaciones, desde interfaces inteligentes hasta visión artificial e inteligencia artificial.

La oferta de dispositivos programables de Intel abarca desde el rango bajo hasta el extremadamente alto, desde las FPGA tradicionales hasta las FPGA de SoC. Como se muestra, para crear diseños con estos dispositivos, Intel y otros terceros ofrecen un poderoso conjunto de kits de desarrollo y herramientas para atender las necesidades de los desarrolladores de hardware, los desarrolladores de software y los creadores de sistemas de inteligencia artificial y visión por computador.

Más lecturas

- Fundamentos de las FPGA: ¿Qué son las FPGA y por qué son necesarias?

- Fundamentos de las FPGA - Parte 2: Introducción a las FPGA de semiconductores en red

- Fundamentos de las FPGA - Parte 3: Introducción a las FPGA de Microchip Technology

- Fundamentos de las FPGA - Parte 4: Introducción a las FPGA de Xilinx

- FPGA 101: Una guía para principiantes

- Implemento de baja potencia y alto rendimiento de computación de punta usando FPGA habilitadas para Quantum de Efinix

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.