Utilice la memoria ferroeléctrica para mejorar la confiabilidad de las aplicaciones automotrices

Colaboración de Editores de DigiKey de América del Norte

2019-06-28

La memoria no volátil (NVM) desempeña un papel clave en casi todos los diseños de sistemas integrados, pero muchos diseños tienen requisitos de memoria no volátiles cada vez más estrictos en términos de velocidad de acceso, escritura de datos, retención de datos y bajo consumo. Este es cada vez más el caso de las aplicaciones automotrices en las que los diseñadores buscan incorporar características más avanzadas, como los sistemas avanzados de asistencia al conductor (ADAS), que son de misión crítica.

Para garantizar un funcionamiento seguro y confiable de estos sistemas, los diseñadores deben analizar más de cerca la memoria ferroeléctrica avanzada de acceso aleatorio (F-RAM) como una opción de memoria NVM de grado automotriz de bajo consumo que es confiable, utiliza poca energía y es más rápida que las soluciones de memoria NVM actuales.

Este artículo analiza las características clave de la tecnología F-RAM y describe cómo los desarrolladores pueden utilizar dos soluciones F-RAM de Cypress Semiconductor para mejorar la confiabilidad de los sistemas ADAS, y usarlos como un proxy para el uso de F-RAM en otras aplicaciones de misión crítica.

Requisitos para memorias NVM automotrices

Las aplicaciones de seguridad automotriz personifican la tendencia de la industria a la integración de sensores más avanzados con mayor resolución y velocidades de actualización más rápidas. Los subsistemas automotrices, como los sistemas ADAS, las unidades de control electrónico (ECU) y los registradores de datos de eventos (EDR), continúan evolucionando, apoyados en conjuntos complejos de datos recopilados de una amplia matriz de sensores. Cualquier pérdida de datos o incluso un acceso lento a estos puede comprometer la seguridad del sistema, el vehículo y sus pasajeros.

En los diseños de sistemas ADAS, por ejemplo, el tiempo necesario para escribir en la Memoria Programable y Borrable de Sólo Lectura (EEPROM) puede causar un retraso potencialmente desastroso en las maniobras automáticas diseñadas para evitar riesgos detectados. En los diseños de velocidad de datos mejorada, el rendimiento de escritura lento puede causar que se pierdan datos críticos del sensor si falla el suministro de energía durante un accidente vehicular, lo que probablemente elimine los datos necesarios para comprender la causa raíz del accidente.

Características de la memoria NVM F-RAM

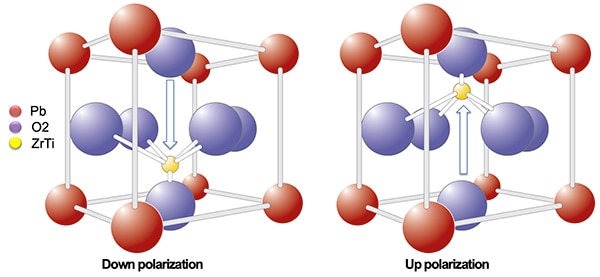

Los dispositivos de memoria construidos con tecnología F-RAM proporcionan una alternativa de memoria NVM efectiva que puede satisfacer la creciente demanda y los requisitos de rendimiento para un almacenamiento de datos y un acceso de alta velocidad confiables. Los dispositivos están fabricados con titanato de circonato de plomo (Pb [ZrxTi1 − x] O3), también conocido simplemente como PZT. El PZT posee la característica única de que la vacancia del metal (catión) incrustada dentro del cristal PZT alcanzará uno de los dos estados de polarización posibles, hacia arriba o hacia abajo, siguiendo la dirección del campo eléctrico aplicado (Figura 1).

Figura 1: La tecnología F-RAM aprovecha las ventajas de dos estados de energía igualmente estables exhibidos por los materiales PZT cuando se los somete a un campo eléctrico. (Fuente de la imagen: Cypress Semiconductor)

Figura 1: La tecnología F-RAM aprovecha las ventajas de dos estados de energía igualmente estables exhibidos por los materiales PZT cuando se los somete a un campo eléctrico. (Fuente de la imagen: Cypress Semiconductor)

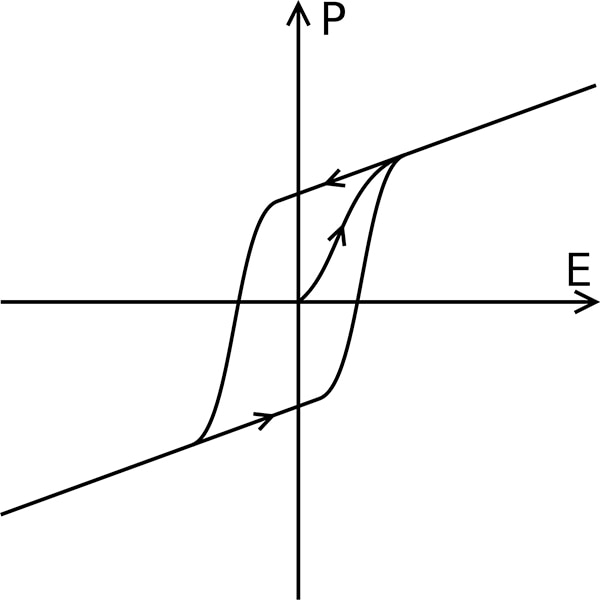

Debido a que ambos son estados iguales de baja energía, el catión permanecerá fijo en su estado de polarización más reciente cuando se elimine el campo eléctrico (Figura 2). Tras la aplicación de un campo eléctrico positivo o negativo, el catión volverá a pasar rápidamente al estado de polarización apropiado siguiendo un ciclo de histéresis característico similar al que se encuentra en los materiales ferromagnéticos.

Figura 2: Los materiales PZT siguen un ciclo de histéresis característico cuando se cambia entre dos estados de polarización estables en respuesta a un campo eléctrico aplicado. (Fuente de la imagen: WikiMedia Commons / CC-BY-SA-3.0)

Figura 2: Los materiales PZT siguen un ciclo de histéresis característico cuando se cambia entre dos estados de polarización estables en respuesta a un campo eléctrico aplicado. (Fuente de la imagen: WikiMedia Commons / CC-BY-SA-3.0)

Las características de la tecnología F-RAM se traducen directamente en una serie de beneficios para los dispositivos de memoria NVM fabricados con esta tecnología. Debido a que ambos estados de energía PZT son igualmente estables, el catión permanecerá en su última posición durante décadas o posiblemente siglos, lo que resulta en tasas de retención de datos sin precedentes en dispositivos de memoria NVM F-RAM basados en PZT. Además, debido a que esta tecnología se basa en la posición del catión en lugar de basarse en los mecanismos de almacenamiento de carga de otras tecnologías NVM, los dispositivos F-RAM son inherentemente tolerantes a la radiación y son inmunes a las alteraciones de un solo evento de la radiación ionizante.

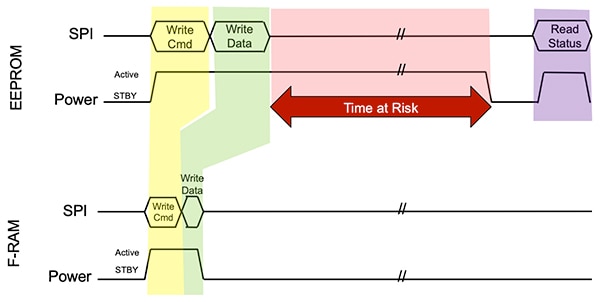

Más allá de sus ventajas para el almacenamiento a largo plazo, la tecnología F-RAM mejora el rendimiento dinámico de los dispositivos de memoria NVM. La transición de estado es muy rápida y requiere poca energía, lo que supera una limitación fundamental asociada con el uso de Memoria Programable y Borrable de Sólo Lectura o Memoria Flash en aplicaciones de misión crítica. La Memoria Programable y Borrable de Sólo Lectura y los dispositivos flash requieren un "tiempo de asimilación de la información" significativo asociado con el almacenamiento de datos en búfer o memoria intermedia durante sus ciclos de escritura relativamente lentos. Este retraso adicional en el ciclo de escritura da como resultado un período en el que los datos pueden estar en riesgo y perderse por completo si falla el suministro de energía antes de que la operación finalice con la verificación final del estado de lectura (Figura 3).

Figura 3: La necesidad de un tiempo prolongado de asimilación de información (resaltado en rojo) durante las operaciones de Memoria Programable y Borrable de Sólo Lectura o de escritura rápida se traduce en un período de tiempo significativo en el que los datos permanecen en riesgo en comparación con los dispositivos F-RAM. (Fuente de la imagen: Cypress Semiconductor).

Figura 3: La necesidad de un tiempo prolongado de asimilación de información (resaltado en rojo) durante las operaciones de Memoria Programable y Borrable de Sólo Lectura o de escritura rápida se traduce en un período de tiempo significativo en el que los datos permanecen en riesgo en comparación con los dispositivos F-RAM. (Fuente de la imagen: Cypress Semiconductor).

Para explicar los ciclos de escritura más lentos en la Memoria Programable y Borrable de Sólo Lectura o en la Memoria Flash, los desarrolladores que esperan mitigar los efectos de las fallas de energía han necesitado agregar capacitores grandes o baterías junto con los reguladores de voltaje apropiados para mantener el voltaje de suministro de memorias NVM el tiempo suficiente para completar las operaciones de escritura. En contraste, los F-RAM como los dispositivos Excelon-Auto de Cypress Semiconductor operan a la velocidad del bus durante las operaciones de escritura, lo que reduce en gran medida la pérdida de datos críticos y elimina la necesidad de fuentes de energía suplementarias en el diseño.

Dispositivos F-RAM de grado automotriz.

Funcionalmente similares a las Memorias Programables y Borrables de Sólo Lectura en serie y a las Memorias Flash en serie, los dispositivos Excelon ™-Auto F-RAM están diseñados para cumplir con los requisitos de las aplicaciones de misión crítica para una memoria NVM confiable y de alto rendimiento. Los diseñadores de sistemas automotrices pueden utilizar estos dispositivos calificados AEC-Q100 para reemplazar otros tipos de memoria, y elegir entre el CY15V102QN para suministros de 1.71 a 1.89 voltios, o el CY15B102QN para suministros de 1.8 a 3.6 voltios. Ambos son dispositivos de 2 megabits (Mbit), lógicamente organizados en 256 Kbits x 8.

En su rango de temperatura de funcionamiento de -40 °C a +125 °C, los dispositivos F-RAM de Excelon tienen una tasa de retención de datos muy superior a la disponible con otras tecnologías de memoria NVM. Por ejemplo, el CY15x102QN puede retener datos por un tiempo estimado de 121 años mientras opera a 85 °C. Como la retención de datos es inversamente proporcional a la temperatura, si se fuerza a los F-RAM a operar en el extremo superior de las temperaturas típicas del motor, por ejemplo, a 95 °C, estas memorias tienen una tasa estimada de retención de datos de 35 años.

Con respecto a la confiabilidad, los F-RAM tienen una duración de ciclo de lectura/escritura de 1013, que es aproximadamente siete órdenes de magnitud mayor que una Memoria Flash o Memoria Programable y Borrable de Sólo Lectura típicas. Como resultado, los desarrolladores que utilizan estos dispositivos F-RAM no necesitan implementar técnicas como la nivelación de desgaste, que distribuye las escrituras entre sectores para tener en cuenta los ciclos de escritura limitados asociados con otras tecnologías de memoria NVM.

Diseño simplificado con F-RAM

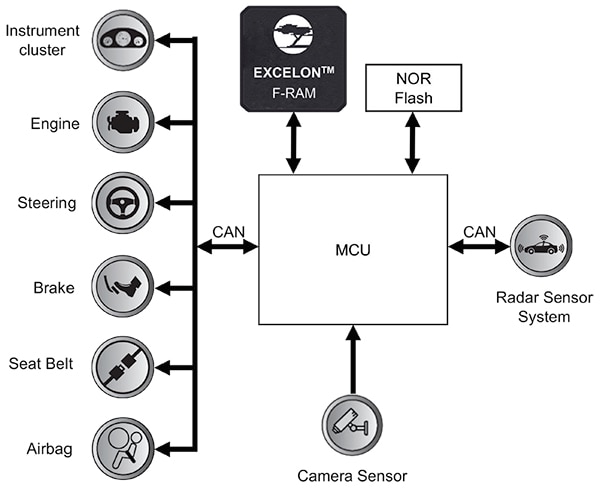

En un diseño típico, los desarrolladores pueden usar estos dispositivos para reemplazar directamente o complementar otros tipos de dispositivos de memoria NVM como NOR flash. En un diseño de sistema ADAS, por ejemplo, los desarrolladores pueden combinar una memoria flash NOR, utilizada para almacenar el firmware, con un dispositivo F-RAM de Excelon capaz de manejar de forma confiable múltiples flujos de datos de los muchos subsistemas automotrices que proporcionan información a las aplicaciones de sistemas ADAS (Figura 4).

Figura 4: Los desarrolladores automotrices de sistemas ADAS pueden combinar dispositivos F-RAM de Excelon para almacenar datos críticos con dispositivos flash NOR que comúnmente se utilizan para almacenar firmware o datos de configuración en diseños basados en microcontroladores (MCU). (Fuente de la imagen: Cypress Semiconductor)

Figura 4: Los desarrolladores automotrices de sistemas ADAS pueden combinar dispositivos F-RAM de Excelon para almacenar datos críticos con dispositivos flash NOR que comúnmente se utilizan para almacenar firmware o datos de configuración en diseños basados en microcontroladores (MCU). (Fuente de la imagen: Cypress Semiconductor)

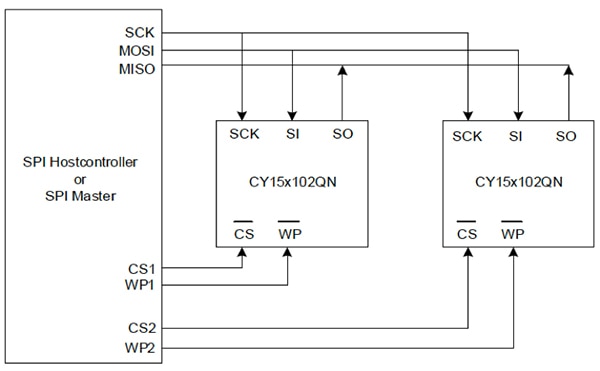

Los desarrolladores pueden colocar fácilmente los dispositivos Excelon F-RAM en un diseño simplemente conectándolos al bus de la interfaz periférica serial (SPI) del procesador central. Diseñados para funcionar como un dispositivo secundario de la interfaz periférica serial (SPI), los F-RAM CY15x102QN pueden admitir velocidades de reloj SPI de hasta 50 megahercios (MHz). En una configuración de hardware típica, los desarrolladores conectan las entradas en serie (SI) y las salidas en serie (SO) del F-RAM a las líneas de Salida de datos del Maestro y Entrada de datos al secundario (MOSI) y Entrada de datos al Maestro y Salida de datos al secundario (MISO) del maestro de la interfaz periférica serial (SPI), respectivamente. Las conexiones a las respectivas líneas de reloj de serie (SCK) y selección de chip (/CS) completan la interfaz de hardware. Los desarrolladores pueden combinar varios dispositivos para compartir el bus SPI del host (Figura 5).

Figura 5: Los desarrolladores pueden usar un bus SPI compartido para conectar un procesador host con uno o más dispositivos F-RAM CY15x102QN. (Fuente de la imagen: Cypress Semiconductor)

Figura 5: Los desarrolladores pueden usar un bus SPI compartido para conectar un procesador host con uno o más dispositivos F-RAM CY15x102QN. (Fuente de la imagen: Cypress Semiconductor)

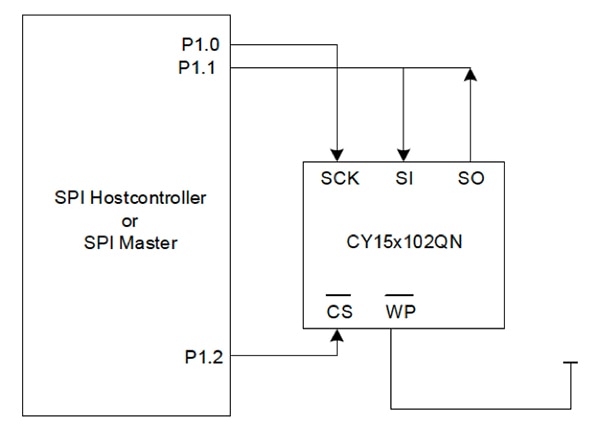

Para microcontroladores (MCU) sin capacidades de interfaz periférica serial (SPI), los dispositivos CY15x102QN son compatibles con una alternativa simple para emular la interfaz de hardware SPI mediante el pin de entrada y salida de uso general (GPIO) del microcontrolador para conectarse al F-RAM. Los desarrolladores pueden implementar esta interfaz y utilizar solo tres pines de entrada y salida de uso general (GPIO) mediante el mismo pin para las líneas de datos de entrada en serie (SI) y salida en serie (SO) del F-RAM (Figura 6).

Figura 6: Para un microcontrolador sin capacidad de interfaz periférica serial (SPI) nativa, los desarrolladores pueden simplemente usar la entrada y salida de uso general del microcontrolador para emular el protocolo de interfaz periférica serial (SPI) y acceder a un F-RAM serial CY15x102QN. (Fuente de la imagen: Cypress Semiconductor)

Figura 6: Para un microcontrolador sin capacidad de interfaz periférica serial (SPI) nativa, los desarrolladores pueden simplemente usar la entrada y salida de uso general del microcontrolador para emular el protocolo de interfaz periférica serial (SPI) y acceder a un F-RAM serial CY15x102QN. (Fuente de la imagen: Cypress Semiconductor)

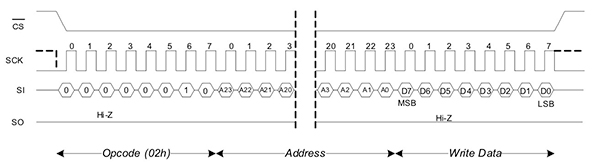

En el protocolo de interfaz periférica serial (SPI) estándar, un maestro inicia una transacción a través de la reducción la selección de chip (/CS). Luego de que su selección de chip (/CS) baja, el F-RAM interpreta el siguiente byte como un código de operación. Por ejemplo, una operación de escritura sigue el código de operación de escritura estándar de la interfaz periférica serial (SPI) (02h) con la dirección de tres bytes y los bytes de datos (Figura 7).

Figura 7: Los dispositivos F-RAM Cypress CY15x102QN son compatibles con los códigos de operación y los protocolos de la interfaz periférica serial (SPI) estándar, lo que permite a los desarrolladores realizar fácilmente escrituras con retraso cero al enviar el código de operación de escritura (02h), la dirección y los datos en secuencia. (Fuente de la imagen: Cypress Semiconductor)

Figura 7: Los dispositivos F-RAM Cypress CY15x102QN son compatibles con los códigos de operación y los protocolos de la interfaz periférica serial (SPI) estándar, lo que permite a los desarrolladores realizar fácilmente escrituras con retraso cero al enviar el código de operación de escritura (02h), la dirección y los datos en secuencia. (Fuente de la imagen: Cypress Semiconductor)

Para los F-RAM CY15x102QN de 2 Mbit, la dirección es una secuencia de tres bytes con los seis bits superiores ignorados. Cypress recomienda establecer en cero estos seis bits superiores para permitir, en el futuro, una transición fácil a dispositivos F-RAM de mayor capacidad.

Una operación de lectura sigue el mismo protocolo. Después de recibir la dirección y el código de operación de lectura estándar (03h), el dispositivo F-RAM transmite los bytes de datos en forma secuencial en salida en serie (SO), lo que automáticamente incrementa la dirección de la memoria mientras la selección de chip (/CS) permanece baja y las señales del reloj continúan. En consecuencia, los desarrolladores pueden realizar una lectura masiva simplemente al mantener baja la selección de chip (/CS) y continuar emitiendo señales de reloj (SCK) hasta que se lea el número requerido de bytes de datos.

Los dispositivos F-RAM CY15x102QN también admiten una función de lectura rápida compatible con la Memoria Flash en serie. Al seguir la dirección y el código de operación de lectura rápida (0Bh), el host de interfaz periférica serial (SPI) envía un byte ficticio para emular la latencia de lectura flash. Después de recibir el byte ficticio, el dispositivo F-RAM responde con los datos solicitados. Las operaciones de lectura rápida también pueden realizar lecturas masivas utilizando el mismo mecanismo que las lecturas estándar.

Protección de escritura

Junto con la lógica de control de la interfaz periférica serial (SPI), los F-RAM CY15x102QN proporcionan mecanismos adicionales para identificar el dispositivo y para proteger contra escritura la matriz F-RAM.

Los desarrolladores pueden emitir códigos de operación de interfaz periférica serial (SPI) para acceder a la ID del dispositivo y a la ID única de sólo lectura de un dispositivo CY15x102QN que proporcionan información sobre el fabricante, la densidad de la memoria y la revisión de la pieza. Los desarrolladores también pueden establecer un registro de número de serie de lectura/escritura de ocho bytes para asociar un F-RAM con un sistema o configuración en particular.

Para la protección F-RAM, el dispositivo proporciona mecanismos de software y hardware. Para la protección de datos durante la fabricación, un sector especial de 256 bytes está diseñado para mantener la integridad de los datos a través de hasta tres ciclos de soldadura por reflujo estándar. Para la protección durante las operaciones normales, el dispositivo utiliza un pestillo de habilitación de escritura (WEL) para proteger la matriz F-RAM de escrituras inadvertidas. En el encendido, el pestillo (WEL) se borra de forma predeterminada, lo que requiere que el desarrollador emita el código de habilitación de escritura (WREN) (06h) antes de realizar las operaciones de escritura.

En el registro de estado del dispositivo, un par de bits de protección de bloque (BP), BP0 y BP1, permite a los desarrolladores proteger la memoria en todo el rango de direcciones (BP1 = 1, BP0 = 1), solo en la mitad superior de la memoria (BP1 = 1, BP0 = 0), o solo en el cuarto superior de la memoria (BP1 = 0, BP0 = 1).

Los desarrolladores pueden usar el pin de protección contra escritura (/WP) del hardware para evitar que el software modifique los bits de protección de bloque (BP) durante las operaciones normales. Aquí, los desarrolladores configuran el bit de habilitación de protección contra escritura (WPEN) en el registro de estado y envían el pin de protección contra escritura (/WP) bajo para bloquear el registro de estado.

Administración de suministro

En las operaciones normales, la eficiencia energética inherente en la tecnología F-RAM generalmente produce un consumo de corriente para el CY15V102QN (VDD 1.71 a 1.89 voltios) a solo 5.0 miliamperios (mA) para operaciones a la velocidad máxima de reloj de 50 MHz. Los desarrolladores pueden reducir la frecuencia del reloj para un mayor ahorro de energía, de modo que los consumos de corriente bajen a aproximadamente 0.4 mA a 1 MHz para el CY15V102QN. El consumo de corriente con CY15B102QN (VDD 1.8 a 3.6 voltios) es solo ligeramente superior a 6.0 mA a 50 MHz y 0.5 mA a 1 MHz.

Para períodos prolongados de inactividad, los desarrolladores reducen significativamente el consumo de energía por medio del uso de los códigos de operación de interfaz periférica serial (SPI) para configurar los dispositivos CY15x102QN en tres modos de bajo consumo:

- Modo de espera con un consumo de corriente típico de 2.7 microamperios (μA) para el CY15V102QN o 3.2 μA para CY15B102QN

- Modo de pérdida de potencia profunda a 1.1 μA para el CY15V102QN o 1.3 μA para CY15B102QN

- Modo de hibernación a 0.1 μA para cualquiera de las dos partes.

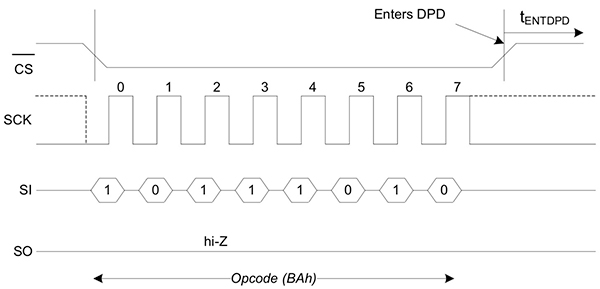

Los dispositivos CY15x102QN cambian automáticamente al modo de espera cada vez que el host de interfaz periférica serial (SPI) establece selección de chip (/CS) alta al final de una secuencia de código de operación. Para cambiar el dispositivo a los modos de hibernación o de pérdida de potencia profunda, el host SPI utiliza el protocolo de código de operación SPI. Específicamente, el host SPI cambia a uno de los dos modos de potencia más bajos al establecer primero la selección de chip baja, luego enviar un código de operación especial para pérdida de potencia profunda (BAh) o hibernación (B9h), y finalmente configurar la selección de chip alta (Figura 8).

Figura 8: Mientras que los dispositivos F-RAM CY15x102QN ingresan automáticamente al modo de espera luego de una secuencia de códigos de operación, los desarrolladores pueden ponerlos en modos de potencia incluso más bajos, como el modo de pérdida de potencia profunda (DPD), a través del procedimiento normal de código de operación SPI. (Fuente de la imagen: Cypress Semiconductor)

Figura 8: Mientras que los dispositivos F-RAM CY15x102QN ingresan automáticamente al modo de espera luego de una secuencia de códigos de operación, los desarrolladores pueden ponerlos en modos de potencia incluso más bajos, como el modo de pérdida de potencia profunda (DPD), a través del procedimiento normal de código de operación SPI. (Fuente de la imagen: Cypress Semiconductor)

Cuando el host SPI establece la selección de chip alta luego de enviar el código de operación de bajo consumo apropiado, el dispositivo F-RAM CY15x102QN ingresa en el modo de bajo consumo solicitado en aproximadamente 3 μs.

Desde el modo de espera, los F-RAM de Cypress regresan inmediatamente al modo activo cuando la selección de chip baja para iniciar la siguiente secuencia de código de operación. Desde el modo de hibernación o de pérdida de potencia profunda, los F-RAM también vuelven al modo activo después de que la selección de chip baja, pero con un breve retraso de aproximadamente 10 μs para el modo de pérdida de potencia profunda, o 450 μs del modo de hibernación.

Conclusión

La necesidad de una memoria NVM confiable, rápida, de baja potencia y alto rendimiento se ha vuelto cada vez más importante en una amplia gama de aplicaciones que dependen de los datos provenientes de una creciente matriz de sensores. En áreas de misión crítica, como las aplicaciones de sistemas ADAS para automóviles, la pérdida de datos puede degradar significativamente los mecanismos de seguridad diseñados para proteger el vehículo y sus ocupantes.

Con los dispositivos F-RAM de Cypress Semiconductor, los desarrolladores pueden agregar fácilmente una memoria NVM que puede almacenar datos críticos de manera confiable durante décadas y sin sacrificar el rendimiento ni los requisitos de bajo consumo.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.